Flip-Flop Tipo D SN74LS175

$ 2.700,0 +IVA

Quad D-Flip-Flop SN74LS175: cuatro biestables tipo D con salidas Q/Q̅, reloj y reset comunes para aplicaciones digitales.

10 disponibles

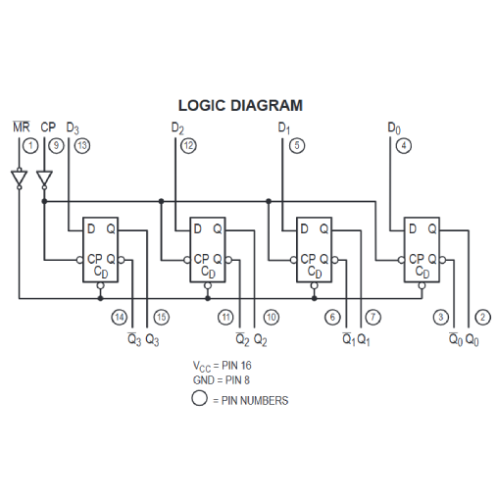

El Quad D-Flip-Flop SN74LS175 es un circuito lógico TTL de alta velocidad diseñado para aplicaciones digitales que requieren almacenamiento sencillo de estados. Este componente contiene cuatro biestables tipo D en un solo encapsulado, con entradas de reloj comunes y una entrada de reinicio maestro asíncrona. Los datos en las entradas D se capturan en la transición de bajada-subida (LOW a HIGH) del reloj, y se proporcionan tanto las salidas Q como las complementarias Q̅, lo que facilita su uso en diseños lógicos requeridos.

En cuanto a los materiales y la fabricación, este dispositivo es parte de la familia LS (Low-Power Schottky) que utiliza diodos Schottky para ofrecer mayor velocidad de conmutación. Está completamente compatible con otras familias TTL estándar, asegurando durabilidad y confiabilidad en entornos de diseño digital.

Entre sus particularidades destacan: gracias a sus cuatro flip-flops integrados, puede usarse como registro de 4 bits, contador, generador de patrones o almacenamiento temporal en sistemas educativos o de prototipado. El uso de salidas complementarias ofrece flexibilidad adicional para lógica negativa sin componentes adicionales. La entrada de reinicio maestro (Master Reset) permite poner todos los flip-flops en un estado conocido independientemente del reloj o de los datos de entrada.

Este dispositivo es ideal para aprendizaje de lógica digital, proyectos STEM, prototipos de control, módulos de memoria temporal y sistemas de registro e intercambio de datos.

Funciones destacadas de Quad D-Flip-Flop

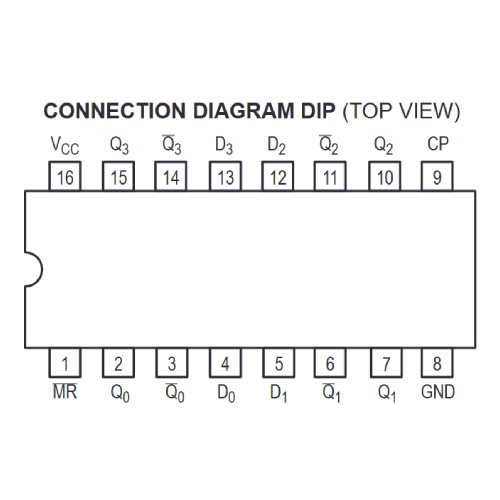

- Cuatro biestables tipo D independientes con entradas D0–D3.

- Salidas tanto Q como Q̅ (complementarias) para cada flip-flop.

- Reloj bufferizado de disparo por flanco de subida (LOW-to-HIGH).

- Reinicio maestro asíncrono (Master Reset, activo LOW) que pone todas las salidas Q a 0 cuando se activa.

- Procesamiento Schottky para alta velocidad y compatibilidad con familias TTL estándar.

Especificaciones técnicas

- Tipo: Cuádruple biestable tipo D (4 × D-Flip-Flop) con reloj común y reinicio común. ti.com+1

- Material / tecnología: TTL Low-Power Schottky (LS) con diodos Schottky. sycelectronica.com.ar+1

- Tamaño / encapsulado típico: 16-pin DIP (VCC pin 16, GND pin 8) pccomponents.com+1

- Tensión de alimentación típica: VCC = 5 V (mínimo ~4.5 V, máximo ~5.5 V) arcade-museum.com+1

- Demora reloj → salida típica: alrededor de 30 ns. sm0vpo.com+1

- Salidas desarrollan tanto Q como Q̅, lo que permite manejo de lógica positiva y negativa.

- Edad recomendada/habilidades desarrolladas: Para usuarios con conocimientos de electrónica digital, uso en proyectos de lógica, micro-controladores, prototipos.

Aplicaciones recomendadas

El SN74LS175 es muy útil en ámbitos educativos, de prototipado y en ingeniería digital. Puede usarse en:

- Proyectos de lógica digital tipo registro de 4 bits, conteo, generación de patrones.

- Sistemas STEM donde se necesita comprender almacenamiento de bit, estados de flip-flops, sincronización de reloj.

- Módulos de interfaz, buffers temporales, latches en micro-controladores.

- Laboratorios de electrónica educativa que enseñan la familia 74LS, señales de reloj, salida complementaria y diseño secuencial.

Datasheet: 74LS175

Para más productos relacionados visita nuestra categoría Circuitos Integrados.

Debes acceder para publicar una valoración.

Valoraciones

No hay valoraciones aún.